时间: 2024-11-09 04:29:34 | 作者: 产品中心

VDD耐压高于35V,输出电压28V以内,无需额定的辅佐绕组供电电路,简化了变压器规划,节约本钱。

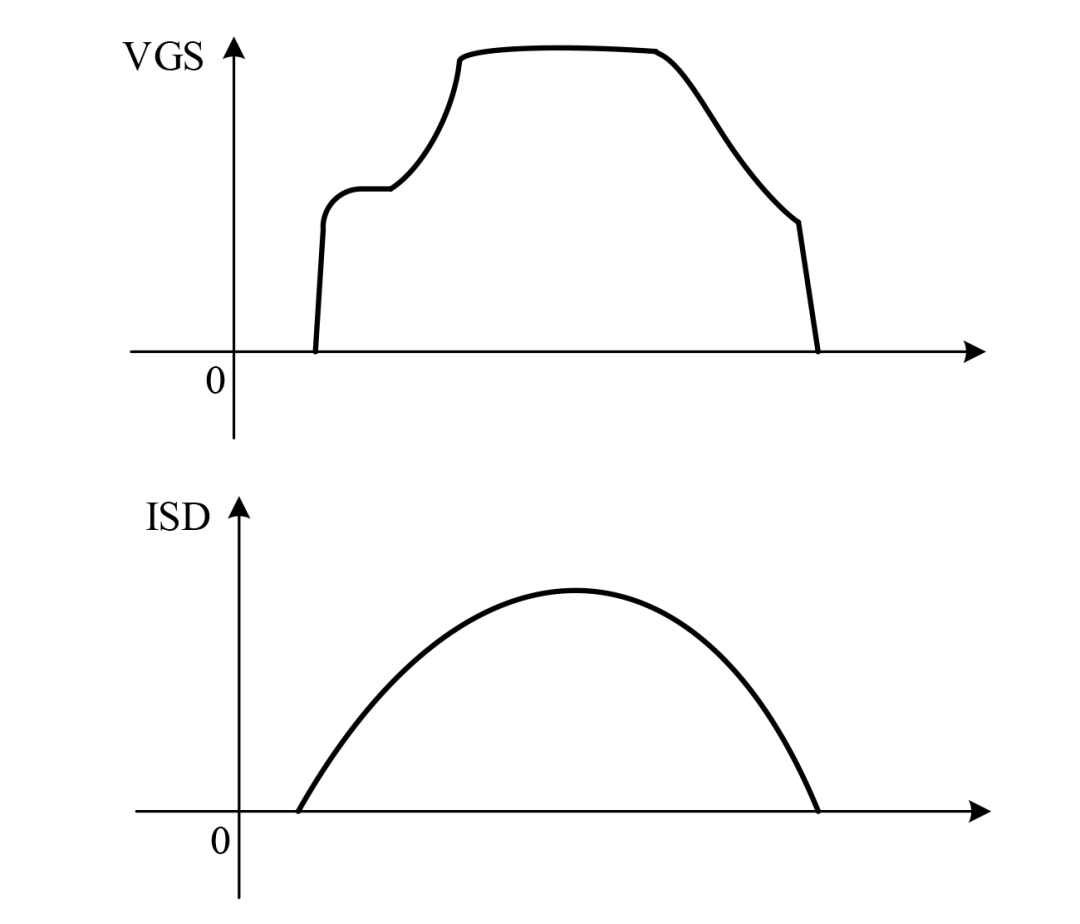

芯片会依据功率MOS电流ISD自适应调整驱动电压VGS,可在CCM下更快关断功率MOS,下降电压应力,支撑500kHz高频化作业。

经过工业级JEDEC牢靠性规范测验,包含HTOL、ESD、Latch-up、TC等11个测验项目。

1►为进步体系ESD才能,芯片供电VDD脚外接RC滤波:R1引荐10Ω,C1引荐1uF。

①芯片VD/VS/VG脚要接近对应的MOSFET的漏极、源极和栅极,不与功率走线堆叠;